RISC-V Tech Market Size and Share

RISC-V Tech Market Analysis by ���ϲ�����

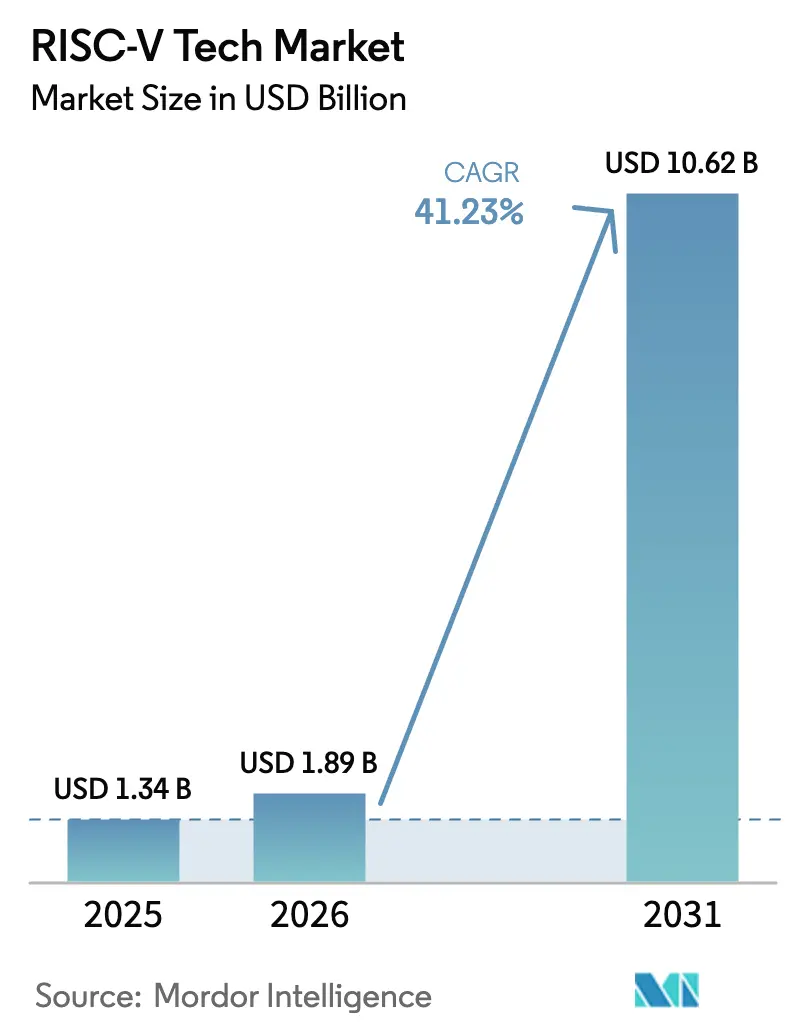

The RISC-V tech market size is projected to expand from USD 1.34 billion in 2025 and USD 1.89 billion in 2026 to USD 10.62 billion by 2031, registering a CAGR of 41.23% between 2026 to 2031. Sustained public funding for sovereign processor programs, rapid adoption of open-standard cores in cloud accelerators, and growing preference for royalty-free architectures in cost-sensitive electronics anchor this expansion. Governments in China, India, Saudi Arabia, and the European Union channel billions of dollars into domestic designs that avoid proprietary licensing. Hyperscale data-center operators deploy RISC-V in inference tiles to reduce power budgets and total cost of ownership, while automotive suppliers integrate open cores in domain controllers to consolidate advanced driver-assistance, infotainment, and body functions. Together, these factors keep the RISC-V tech market on a steep growth curve, encourage software-toolchain maturity, and attract venture capital to verification and chiplet ecosystems.

Key Report Takeaways

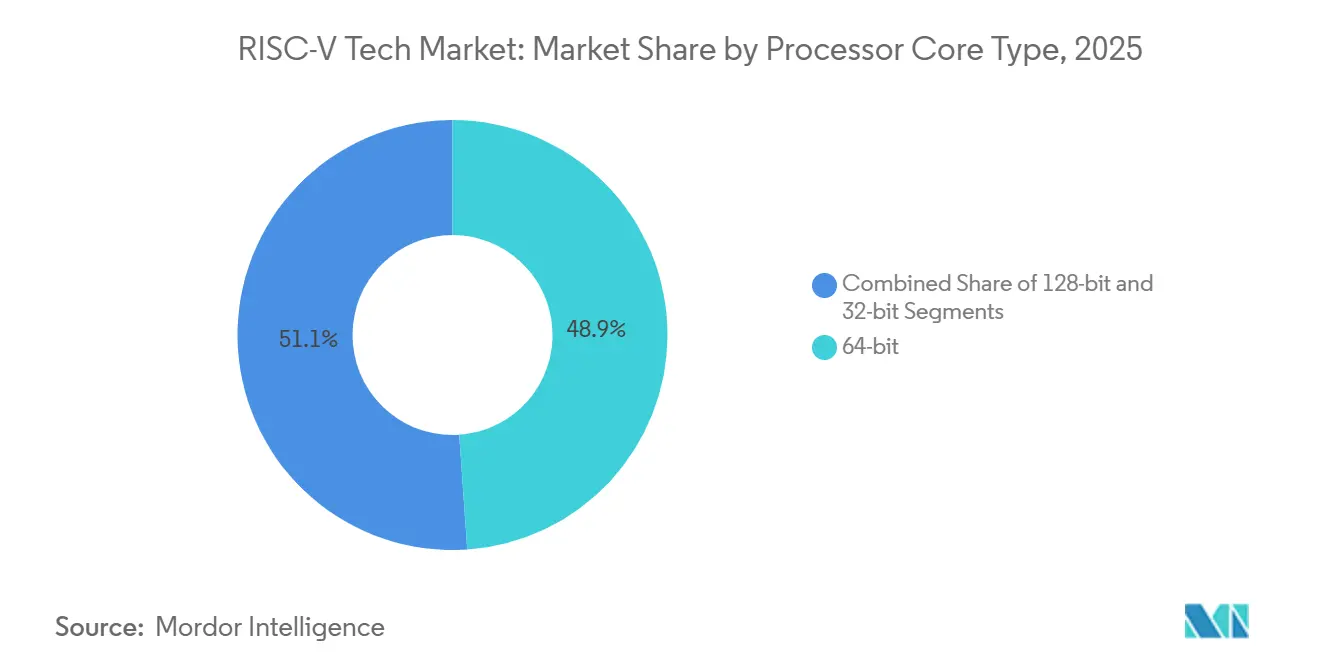

- By processor core type, 64-bit cores led with 48.91% of RISC-V tech market share in 2025, while 128-bit cores are projected to expand at a 41.88% CAGR through 2031.

- By core IP business model, royalty-free licensed cores accounted for 39.56% of the RISC-V tech market size in 2025, whereas commercial royalty-bearing cores show the highest projected CAGR at 41.82% through 2031.

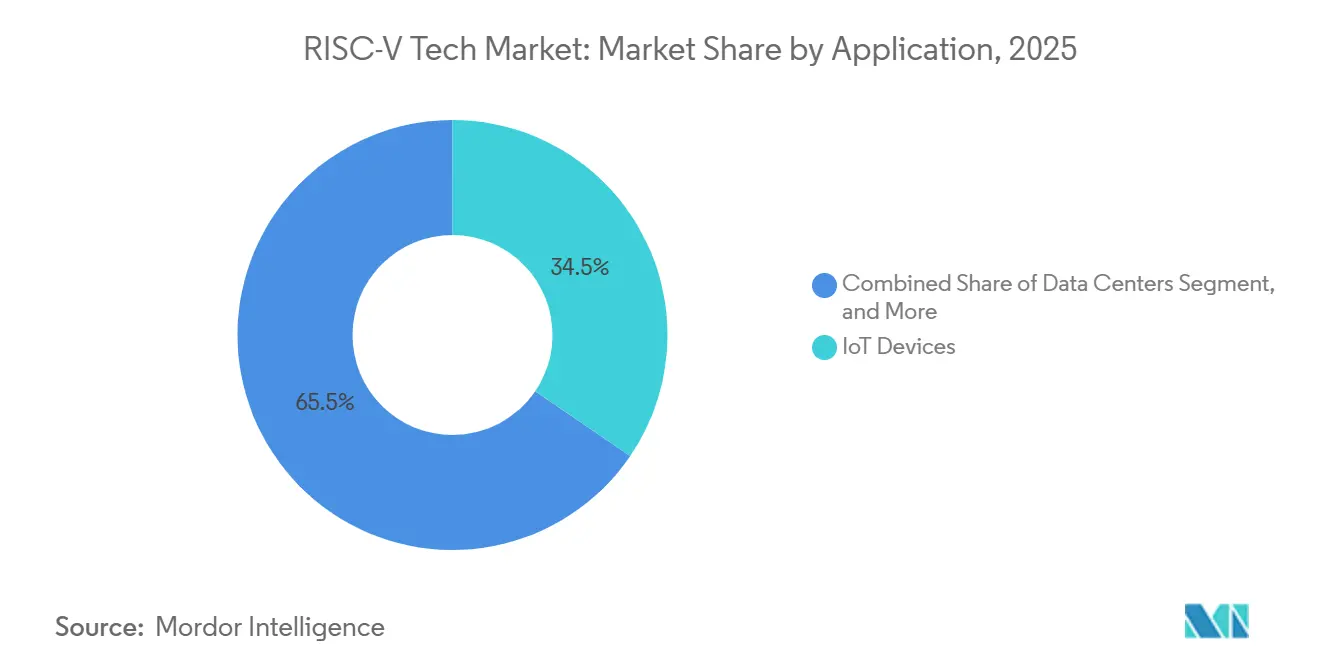

- By application, IoT devices held 34.52% revenue share in 2025; data centers record the fastest growth at a 42.64% CAGR between 2026-2031.

- By end-user industry, consumer electronics captured 28.71% of revenue in 2025, but automotive and transportation is forecast to accelerate at a 42.89% CAGR to 2031.

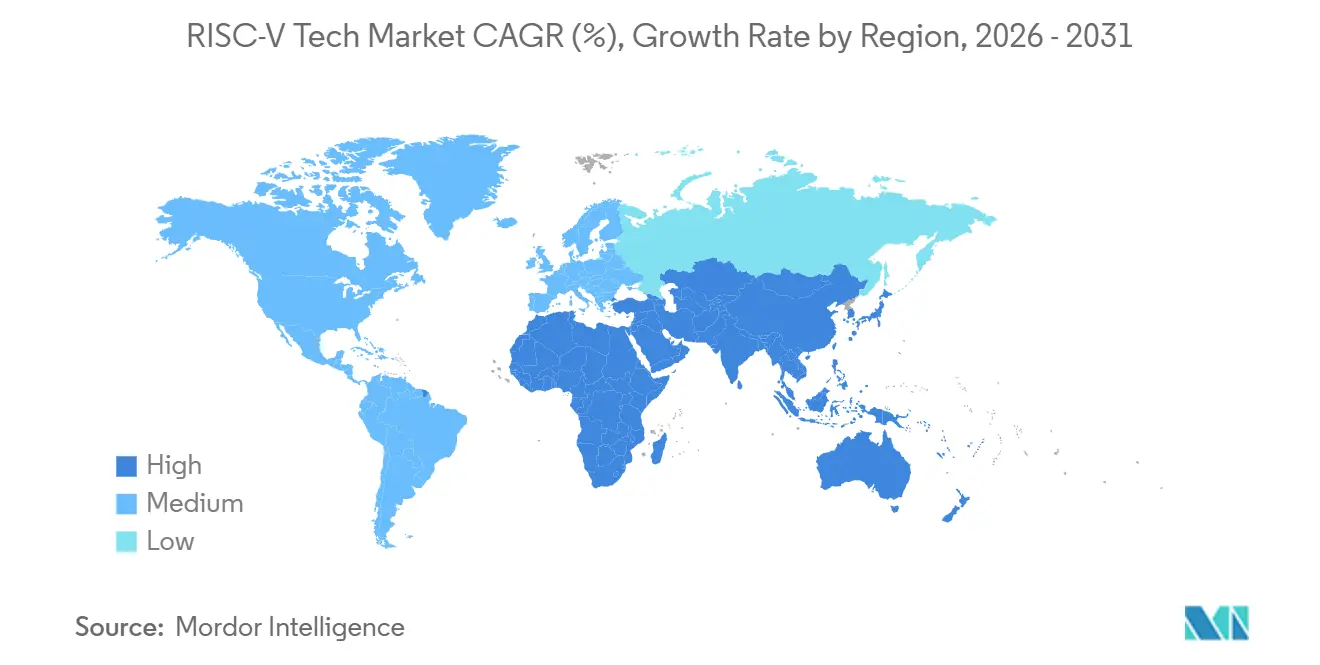

- By geography, Asia-Pacific commanded 42.33% of 2025 value, and the Middle East presents the quickest regional trajectory at a 42.24% CAGR over 2026-2031.

Note: Market size and forecast figures in this report are generated using ���ϲ�����’s proprietary estimation framework, updated with the latest available data and insights as of January 2026.

Global RISC-V Tech Market Trends and Insights

Drivers Impact Analysis

| Driver | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Rapid Proliferation of AI and ML-Centric Edge Workloads | +8.5% | Global, with concentration in North America and Asia-Pacific | Medium term (2-4 years) |

| Software Toolchain Maturity Attracting Tier-1 OEMs | +7.2% | Global, led by North America and Europe | Short term (≤ 2 years) |

| National Chip-Sovereignty Programs | +6.8% | Asia-Pacific core, spillover to Europe and Middle East | Long term (≥ 4 years) |

| Open-Standard IP Accelerating Silicon Time-to-Market | +5.5% | Global | Short term (≤ 2 years) |

| Commercial-Grade Verification Ecosystems | +4.3% | North America and Europe | Medium term (2-4 years) |

| Rise of Chiplet-Based Modular Architectures for Custom SoCs | +3.9% | Global, early adoption in North America and Asia-Pacific | Long term (≥ 4 years) |

| Source: ���ϲ����� | |||

Rapid Proliferation of AI and ML-Centric Edge Workloads

Edge devices now run computer vision and language models that require flexible scalar, vector, and matrix operations in a single core. The RISC-V vector extension lets designers select register lengths from 128 to 2,048 bits, so silicon area scales with workload accuracy requirements. Google’s 2025 Edge TPU refresh used these extensions and cut MobileNet v3 inference latency by 34% compared with a prior ARM Cortex-M55 design.[1]Google Cloud, “Edge TPU Performance Benchmarks,” CLOUD.GOOGLE Europe’s EPAC 1.0 accelerator pairs RISC-V control cores with domain-specific AI tiles and reaches 12 TOPS per watt, confirming that open ISAs meet battery constraints in robotics and autonomous systems. Automotive OEMs follow the same path for in-cabin driver monitoring because vectorized inference fits within strict ISO 26262 budgets without incurring high royalties from proprietary vendors.

Software Toolchain Maturity Attracting Tier-1 OEMs

Adoption accelerated once RISC-V support became first-class in GCC, LLVM, Android, and the Linux kernel. The RISE project delivered a unified Android runtime and Kubernetes layer in 2025, erasing middleware gaps that once stalled Samsung and Xiaomi.[2]RISC-V International, “RISE Project Milestones,” RISC-V.ORG Ubuntu 24.04 LTS then shipped with server-grade RV64 ports, giving cloud operators a ready migration path from x86 and ARM. Enterprise EDA tools kept pace: Siemens Tessent and Synopsys VC Formal added RISC-V-native flows, enabling automotive suppliers to meet ISO 26262 checkpoints without manual workarounds. With full-stack support in place, tier-1 OEMs now view the architecture as production-ready rather than experimental.

National Chip-Sovereignty Programs

Export-control pressure and supply-chain shocks push governments to fund processors they can license freely. China’s State Council earmarked CNY 15 billion (USD 2.1 billion) to replace foreign ISAs in consumer and industrial chips by 2027. India’s Vega initiative redirected public procurement toward home-grown RISC-V devices, moving an estimated USD 450 million of annual orders away from legacy suppliers. The EU Chips Act set aside EUR 1.2 billion (USD 1.3 billion) for pilot lines that Fraunhofer and CEA-Leti will use to build ASIL-D automotive cores. Saudi Arabia’s Public Investment Fund invested USD 500 million in SiFive to help NEOM’s smart-city infrastructure avoid foreign licensing risks. These country-level mandates guarantee multiyear demand and reassure domestic talent that open ISAs offer stable career paths.

Open-Standard IP Accelerating Silicon Time-to-Market

Proprietary ISA negotiations often last a year and carry per-unit royalties that erode margins in cost-sensitive segments. RISC-V’s Apache or BSD licenses skip those delays, letting startups tape out chips in 12-15 months. Esperanto’s 1,088-core ET-SoC-1 reached silicon in early 2025 without the USD 25-30 million in ARM fees that a similar design would incur. RISC-V International’s Fast Track program provides pre-verified core bundles and test suites, reducing design validation from 6 months to a few weeks. Lattice’s CertusPro-NX FPGAs embed royalty-free soft cores, so industrial customers can prototype control logic immediately and avoid upfront IP costs. Shorter cycles and lower fees attract venture funding and expand the addressable customer base beyond top-tier semiconductor houses.

Restraints Impact Analysis

| Restraint | (~) % Impact on CAGR Forecast | Geographic Relevance | Impact Timeline |

|---|---|---|---|

| Fragmented ISA Extensions Increasing Software Complexity | -4.2% | Global | Short term (≤ 2 years) |

| Limited Backward-Compatibility Guarantees versus ARM ISA | -2.8% | Global, acute in North America and Europe | Medium term (2-4 years) |

| IP Indemnification and Patent-Litigation Uncertainties | -2.5% | Global, most acute in North America | Medium term (2-4 years) |

| Scarcity of Experienced RISC-V-Ready EDA Talent | -1.9% | Global, concentrated in Asia-Pacific | Short term (≤ 2 years) |

| Source: ���ϲ����� | |||

Fragmented ISA Extensions Increasing Software Complexity

Freedom to add custom instructions boosts hardware innovation but multiplies software maintenance. By December 2025, vendors implemented divergent subsets of 42 ratified extensions, forcing Google to keep seven Android runtime builds for RISC-V phones, a burden that delayed feature parity by two quarters.[3]AUTOSAR, “RISC-V Support in Release R23-11,” AUTOSAR.ORG The Linux kernel needed 18 RISC-V configuration profiles in version 6.7, four times the ARM64 count, which raised continuous-integration overhead for Debian and Fedora maintainers. AUTOSAR’s R23-11 release specifies a baseline RV64GC profile but still allows optional extras, so in-vehicle ECUs from different suppliers can fall out of binary sync. Such fragmentation slows over-the-air updates and increases OEMs' lifetime support costs.

Limited Backward-Compatibility Guarantees Versus ARM ISA

ARM promises that older binaries run unchanged on newer Cortex generations, but RISC-V’s forward-only model lacks equivalent safeguards. The shift from draft RVV 0.7 to ratified RVV 1.0 broke early vector binaries and forced Alibaba to rebuild its Xuantie software stack, a resource-intensive task that still lingers in developer memory. Red Hat labels RISC-V support in RHEL 9.3 as a “technology preview” because long-term ABI stability is not yet certain, which deters Fortune 500 rollouts. The RVA23 profile tries to freeze mandatory extensions, yet adoption stays voluntary, so Ventana’s Veyron V2 targets RVA23 while StarFive’s JH7110 ships with RVA20. Unsettled compatibility expectations make CIOs wary of committing to seven-year support contracts on the architecture.

Segment Analysis

By Processor Core Type: 128-Bit Momentum Underpins AI Expansion

64-bit cores accounted for 48.91% of the RISC-V tech market share in 2025, reflecting their dominance in Linux-capable application processors and mainstream cloud workloads. The 128-bit tier is now the fastest mover, projected to grow at a 41.88% CAGR through 2031 as designers rely on extended vector registers to collapse scalar, vector, and matrix engines into one block. This upgrade removes the need for discrete AI accelerators in edge gateways and domain controllers, trimming the bill of materials and shortening board layouts. The 32-bit slice is used in cost-sensitive microcontrollers such as smart meters and Bluetooth Low Energy sensors, where 64-bit addressing would raise area and power budgets.

A broadened software stack supports all tiers, so OEMs can slot the right core footprint into each product line without rewriting toolchains. Canonical, Red Hat, and SUSE standardized on RV64GC in 2025, giving the 64-bit class reliable server support even as 128-bit profiles mature. Alibaba’s upcoming Xuantie C930 illustrates the upside, pairing 128-bit vectors with a large L3 cache to deliver 45 tera-operations per second for INT8 inference. The ongoing coexistence of 32-, 64-, and 128-bit implementations expands the RISC-V tech market, as each core width targets a distinct price-performance point.

Note: Segment shares of all individual segments available upon report purchase

By Core IP Business Model: Indemnified Licensing Gains Traction

Royalty-free-licensed cores captured 39.56% of 2025 revenue because startups and universities favor zero-fee IP when time-to-prototype outweighs liability exposure. Commercial royalty-bearing cores are on a steeper 41.82% CAGR path as automotive, aerospace, and cloud buyers demand patent indemnification and formal verification credits that open projects rarely supply. SiFive’s X280 bundles safety artifacts and legal cover for more than one thousand claims, proving that buyers will accept a 3-5% royalty when certification risk vanishes.

Open-source cores such as CVA6 and BOOM still power academic designs and at-cost industrial controllers, yet they stall in safety-critical or enterprise servers where warranty clauses dominate procurement checklists. The ongoing shift toward paid packages expands the RISC-V market for vendors able to combine performance leadership with compliance documentation. As insurance carriers tighten product-liability language, boards of directors increasingly push engineers toward indemnified IP even for low-margin devices. That trend narrows the revenue gap between free and licensed models by the decade’s close.

By Application: Data Centers Outpace IoT Volume

IoT devices accounted for 34.52% of application revenue in 2025, after billions of Wi-Fi modules and sensor nodes shipped with tiny RISC-V microcontrollers. Data centers now exhibit the strongest trajectory, with a 42.64% CAGR, because hyperscalers are integrating open-ISA inference tiles that lower power draw and total cost of ownership compared with proprietary GPUs. Meta’s 2026 deployment timeline shows that one cloud operator can absorb millions of cores per year once software stacks stabilize. Cellular infrastructure and 5G handsets add incremental pull, with modem subsystems already moving from ARM Cortex-M to RISC-V for power sequencing and sensor fusion.

The widening footprint inside back-end infrastructure resets value per core at a far higher level than IoT shipments can match. Alibaba Cloud’s 128-core Yitian 710 handles search and log aggregation tasks, saving double-digit energy savings that translate directly into operating-expense relief. As server sockets grow, they drag along a complete software ecosystem that benefits every other form factor, including notebooks and gaming consoles, now in proof-of-concept testing. The resulting mix shift raises average selling prices and lifts the RISC-V tech market size faster than raw unit counts suggest.

Note: Segment shares of all individual segments available upon report purchase

By End-User Industry: Automotive Electrification Catalyzes Uptake

Consumer electronics accounted for 28.71% of 2025 revenue, driven by smartphones, wearables, and smart-home gear that prioritize low silicon costs and long battery life. Automotive and transportation, however, is projected to expand at a 42.89% CAGR through 2031 as domain controllers merge advanced driver assistance, infotainment, and body functions onto shared compute fabrics. Bosch demonstrated the model by pairing RISC-V control clusters with Nvidia GPUs on an ASIL-D platform that reduces semiconductor costs by up to one-fifth.

Functional-safety certification once favored proprietary ISAs with mature collateral, yet in 2025, the first RISC-V cores achieved ISO 26262 deliverables, clearing a decisive obstacle for vehicle launches. Electrification and zonal architectures also make power efficiency and thermal density critical, two metrics where open-ISA cores can be right-sized without extra royalty headroom. These design freedoms invite tier-1 suppliers to build custom silicon in-house rather than buy standalone microcontrollers, and that shift in sourcing strategy broadens RISC-V's market share in the global automotive supply chain. Moderate gains in medical devices, industrial automation, and aerospace add stability, but the volume surge clearly comes from software-defined vehicles.

Geography Analysis

Asia-Pacific accounted for 42.33% of global revenue in 2025, giving the region the largest RISC-V market share among all geographies. China’s state funding, India’s public-sector mandates, and Japan’s consortium investments create a self-reinforcing design ecosystem that spans consumer IoT devices, cloud servers, and automotive domain controllers. Local foundries and design houses in Malaysia and Vietnam add low-cost engineering capacity, helping multinational customers localize open-ISA projects without increasing bill-of-materials costs. Rapid shipment growth in Alibaba T-Head’s IoT cores and India’s Param Rudra supercomputer anchors volume, while regional universities supply a steady pipeline of compiler and verification talent. Combined, these forces keep Asia-Pacific on track for double-digit annual gains through 2031.

The Middle East is the fastest-growing region, with RISC-V revenue projected to grow at a 42.24% CAGR between 2026 and 2031. Saudi Arabia’s Public Investment Fund secured SiFive licenses for NEOM, and the United Arab Emirates’ Mubadala invested in Ventana’s 5-GHz server roadmap, positioning the Gulf as a design and data-center hub. Local initiatives in Egypt and Qatar train thousands of engineers in open-ISA toolchains, shortening project lead times for regional startups. Sovereign wealth capital de-risks early designs by underwriting pilot production, so fabless teams can sample silicon without waiting for export-license clearances. These policies signal intent to build a self-reliant supply chain rather than import proprietary architectures.

North America and Europe grow more slowly yet remain crucial to enterprise adoption because they host the majority of verification, EDA, and cloud software vendors. U.S. hyperscalers deploy RISC-V inference tiles to trim power budgets, while DARPA’s secure-enclave programs steer defense spending toward open cores. The European Union’s EUR 1.2 billion pilot lines at Fraunhofer and CEA-Leti target ISO 26262 automotive certification, which should lift the RISC-V tech market size in the region once parts reach production. South America and Africa stay in early stages, but Brazil’s research grants and South Africa’s smart-grid pilots create beachheads for future expansion.

Competitive Landscape

The top five vendors, namely SiFive, Alibaba T-Head, Andes Technology, Ventana Micro Systems, and StarFive, together commanded about 38% of global revenue in 2025, underscoring a moderately fragmented field. Each player focuses on a distinct performance band: SiFive and Ventana chase high-end cloud and automotive sockets, while Andes and StarFive win cost-sensitive IoT and industrial designs. Alibaba’s in-house cores feed its cloud workload, yet the company also licenses IP to Chinese device makers, adding another competitive dimension.

SiFive’s January 2026 launch of the P870-V vector-cryptography core and Ventana’s USD 300 million Series C raise illustrate how capital flows to performance-centric roadmaps. Andes expanded its N25F licensee count past 80 by bundling low-cost safety packages, and StarFive gained ISO 9001 certification to improve standing with automotive tier-ones. Esperanto, GreenWaves, and Akeana pursue domain-specific arrays that target AI inference or chiplet glue logic, proving that specialization can sidestep head-to-head core battles with larger rivals.

Toolchain vendors hold much of the ecosystem's power. Synopsys, Cadence, and Siemens EDA now ship formal-verification flows that match ARM parity, giving core suppliers ready-made safety collateral for ISO 26262 and DO-254. RISC-V International’s 4,200-member governance model standardizes baseline profiles while allowing companies to propose extensions, balancing innovation with portability. As more enterprise customers demand indemnified IP and long-term software support, vendors that pair high performance with robust warranties are positioned to gain share, but overall competition should remain open given the architecture’s low entry barriers.

RISC-V Tech Industry Leaders

Alibaba Group Holding Limited

Andes Technology Corporation

Antmicro Sp. z o.o.

Bluespec, Inc.

Huawei Technologies Co., Ltd.

- *Disclaimer: Major Players sorted in no particular order

Recent Industry Developments

- January 2026: SiFive launched the P870-V vector-cryptography core on TSMC N3E, targeting data-center encryption appliances.

- December 2025: Ventana raised USD 300 million in Series C funding led by Mubadala to develop 5-GHz server processors in Abu Dhabi.

- November 2025: Alibaba Cloud reported 80% internal workload migration to its 128-core Yitian 710 processor, saving USD 120 million in annual energy costs.

- October 2025: Bosch unveiled Vehicle Computer 3.0, which pairs RISC-V and Nvidia Orin for ISO 26262 ASIL-D level-3 automation.

Global RISC-V Tech Market Report Scope

The RISC-V Tech Market Report is Segmented by Processor Core Type (32-bit, 64-bit, 128-bit), Core IP Business Model (Open-Source Cores, Royalty-Free Licensed Cores, Commercial Royalty-Bearing Cores), Application (Smartphones, 5G Devices, Data Centers, Personal Computers and Game Consoles, Cellular Network Infrastructure, IoT Devices, Other Applications), End-User Industry (Computing and Storage, Communication Infrastructure, Consumer Electronics, Automotive and Transportation, Medical, Aerospace and Military, Industrial, Other End-User Industries), and Geography (North America, South America, Europe, Asia-Pacific, Middle East, Africa). The Market Forecasts are Provided in Terms of Value (USD).

| 32-bit |

| 64-bit |

| 128-bit |

| Open-Source Cores |

| Royalty-Free Licensed Cores |

| Commercial Royalty-Bearing Cores |

| Smartphones |

| 5G Devices |

| Data Centers |

| Personal Computers and Game Consoles |

| Cellular Network Infrastructure |

| IoT Devices |

| Other Applications |

| Computing and Storage |

| Communication Infrastructure |

| Consumer Electronics |

| Automotive and Transportation |

| Medical |

| Aerospace and Military |

| Industrial |

| Other End-User Industries |

| North America | United States | |

| Canada | ||

| Mexico | ||

| South America | Brazil | |

| Argentina | ||

| Rest of South America | ||

| Europe | United Kingdom | |

| Germany | ||

| France | ||

| Italy | ||

| Rest of Europe | ||

| Asia-Pacific | China | |

| Japan | ||

| India | ||

| South Korea | ||

| Rest of Asia-Pacific | ||

| Middle East and Africa | Middle East | United Arab Emirates |

| Saudi Arabia | ||

| Rest of Middle East | ||

| Africa | South Africa | |

| Egypt | ||

| Rest of Africa | ||

| By Processor Core Type | 32-bit | ||

| 64-bit | |||

| 128-bit | |||

| By Core IP Business Model | Open-Source Cores | ||

| Royalty-Free Licensed Cores | |||

| Commercial Royalty-Bearing Cores | |||

| By Application | Smartphones | ||

| 5G Devices | |||

| Data Centers | |||

| Personal Computers and Game Consoles | |||

| Cellular Network Infrastructure | |||

| IoT Devices | |||

| Other Applications | |||

| By End-User Industry | Computing and Storage | ||

| Communication Infrastructure | |||

| Consumer Electronics | |||

| Automotive and Transportation | |||

| Medical | |||

| Aerospace and Military | |||

| Industrial | |||

| Other End-User Industries | |||

| By Geography | North America | United States | |

| Canada | |||

| Mexico | |||

| South America | Brazil | ||

| Argentina | |||

| Rest of South America | |||

| Europe | United Kingdom | ||

| Germany | |||

| France | |||

| Italy | |||

| Rest of Europe | |||

| Asia-Pacific | China | ||

| Japan | |||

| India | |||

| South Korea | |||

| Rest of Asia-Pacific | |||

| Middle East and Africa | Middle East | United Arab Emirates | |

| Saudi Arabia | |||

| Rest of Middle East | |||

| Africa | South Africa | ||

| Egypt | |||

| Rest of Africa | |||

Key Questions Answered in the Report

How fast will global revenue from RISC-V cores grow from 2026-2031?

The RISC-V tech market is projected to expand at a 41.23% CAGR between 2026-2031, reaching USD 10.62 billion by the end of the period.

Which processor core size is expected to gain the most momentum?

128-bit cores will advance at a 41.88% CAGR as vector units remove the need for separate AI accelerators in edge devices.

Why are data-center operators moving to RISC-V?

Hyperscalers report up to 18% lower total cost of ownership and 28% lower latency when RISC-V inference tiles replace proprietary accelerators.

Which region will see the quickest uptake of open-ISA processors?

The Middle East shows the fastest trajectory at a 42.24% CAGR as sovereign funds back local design centers and smart-city deployments.

What drives automotive interest in RISC-V?

Consolidating ADAS, infotainment, and body control on open cores cuts semiconductor bills by 18-22% and supports ISO 26262 safety compliance.

Are commercial IP licenses gaining over royalty-free cores?

Yes, demand for patent indemnification and formal safety deliverables is pushing commercial royalty-bearing cores to grow at 41.82% CAGR.